SeeMos platform is dedicated to active vision and in particular to the early vision process. Thus, the SeeMos platform which constitutes an embedded system is composed of a modular hardware and a software design.

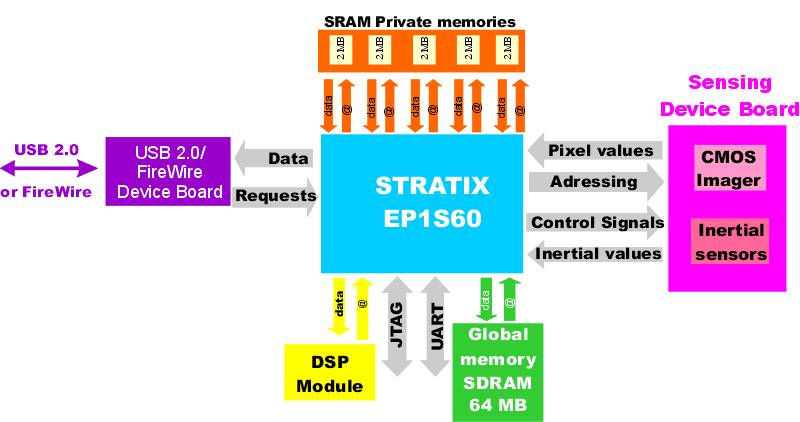

The main feature of this platform is an architecture based on FPGA, CMOS imager, Inertial devices, High speed communication and a DSP-based Codesigned board.

The main purpose of our architecture is to allow the implementation of early vision processes as in the human or primate visual system. In these systems it is well known that the first neural layers (in the retina) pre-filter the visual data flow in order to select only the conspicious information.

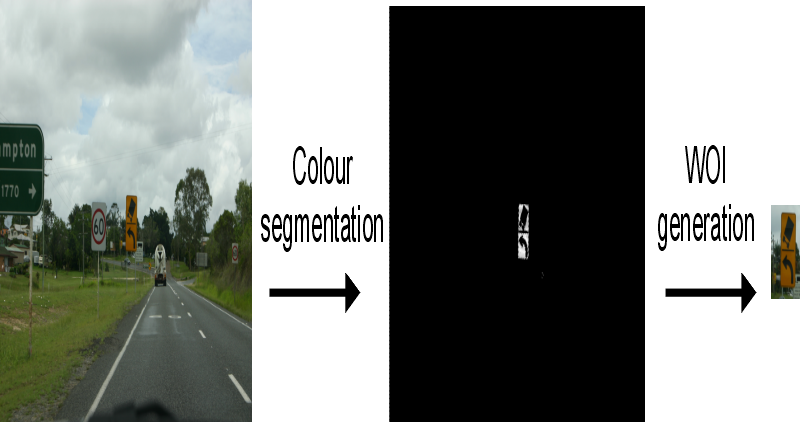

This Prefiltering step needs strong parallelization, on one hand to respect real-time constraints, and on the other hand because of the intrinsic characteristics of the algorithms. For exemple, some classical algorithms in an attention task used to elaborate an efficient saliency map are motion detection, Gabor filters, and color segmentation. However, the characteristics of particular visual tasks may require dedicated image processing and only an FPGA approach allows such flexibility. For architectures such as these, a Stratix EP1S60 from Altera has been chosen. The need for strong parallelization was what led us to connect 5x2MB SRAM synchronous memory blocks. In our approach, the high-level processing has to be performed on a host computer rather than on the embedded system.