Prix Jeunes Chercheurs

3 prix gagnés par nos docteurs à la 27e édition des Prix Jeunes Chercheurs de Clermont-Ferrand :

Prix Clermont Auvergne Innovation pour Guillaume Mougeot, Docteur en Image, système de perception, robotique (ED SPI) pour sa thèse en collaboration avec l'IGReD et Oxford (Nuclear Plant Envelope).

Prix INP Polytech pour Guy Vano Tsamo Tagouche, Docteur en Ingénierie des Matériaux (ED SPI) pour sa thèse.

Prix de la Fondation UCA pour Ismaël Septembre, Docteur en Physique - Milieux denses et matériaux (ED SF) pour sa thèse.

Nous félicitons Sayed Mohammadreza Shetab Bushehri, Docteur en Génie Electrique, Electronique et Systèmes (ED SPI) qui a brillamment défendu la robotique de manipulation des objets déformables.

Plateforme multi-techniques d’élaboration et de caractérisation

L'Institut Pascal, vient de se doter d'un nouveau Système d'Analyse et de Structuration des Surfaces (SASS) grâce aux financements de l'Union Européenne dans le cadre du FEDER, de la Région AURA et avec le soutien de l'UCA.Cette plateforme est dédiée à l’analyse de matériaux organiques et inorganiques avec un volume qui s'étend de la surface à une profondeur d'environ 50-100 Å. Les techniques de caractérisation disponibles sont multiples : AR-XPS, UPS, ARPES, REELS apportant des informations différentes liées à la profondeur d’analyse et à l’interaction du rayonnement électromagnétique avec la matière.

Séminaire axe ISPR

Collaboration Michelin - IP

Dans le cadre d'une collaboration entre l'Institut Pascal et la manufacture Michelin, une démonstration réelle s'est déroulée le jeudi 10 novembre 2022 afin de montrer les capacités d'un véhicule autonome à évoluer à 40 km/h sur une piste particulièrement éprouvante pour les pneumatiques. Cette première démonstration rentre dans un projet plus global qui doit permettre aux deux partenaires de montrer les capacités de ce type de véhicule à réaliser en autonomie certains tests de pneumatiques mais également de travailler sur le développement de nouveaux tests dont certains plus spécifiques pour ces véhicules de demain.

La fête de la science 2022

Pour l'édition 2022 de la Fête de la Science, l'Institut Pascal était présent sur tous ses thèmes de recherche sur des sites différents du campus des Cézeaux. Les démonstrations aux chercheurs en herbe allaient de la plateforme Pavin Solaire, en passant par les véhicules autonomes, les robots et la 3D, les pouvoirs magiques de la lumière noire et sous forme d'un escape game pour les mystères des capteurs de gaz.

Journées robotiques agricoles

Les deux journées techniques du réseau R2M et du projet AgROBOFood co organisées par INRAE, CEA et Institut Pascal ont lieu ces 12 & 13 octobre sur le site de Montoldre autour des thèmes de la navigation, la sécurité et l’intelligence artificielle pour le développement de robots mobiles en agriculture et en environnement ouvert.

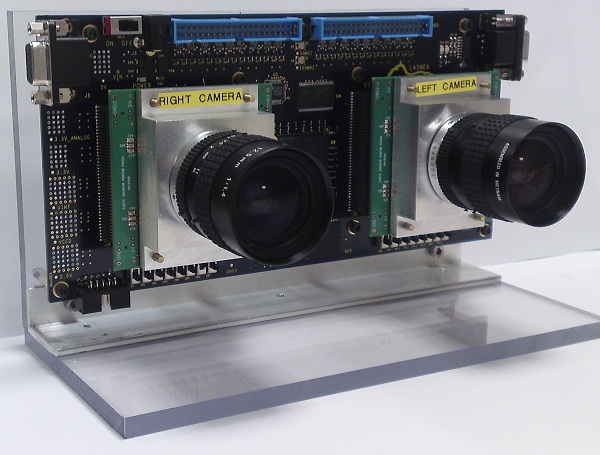

Dream team has developed an architecture of a new smart vision system called BiSeeMos. This smart camera is designed for stereo vision purposes and the implementation of a simple dense stereo vision algorithm. In addition, the architecture has been designed for dedicated parallel algorithms by using a high performance FPGA. This chip provides the user with useful features for vision processing as integrated RAM blocks, embedded multipliers, phase locked loops and plenty of logic elements.

For further information on BiSeeMos architecture including hardware features and design strategies, please read the following article: BiSeeMos. In this article, "Stereo Vision Algorithm Example" is examined in order to demonstrate the efficiency of this platform in real time processing.

More recently two others stereo Smart camera have been done:

-

BiSeeMOS II is lighter the the previous one. The FPGA is EP3C16 with only 1 SRAM Block of 1MWord. Communication link is performed by an embedded USB2.0 chip.

-

BiSeeMOS III is a compromise between the two first ones. It includes a CycloneIII EP3C40 and its size is that of coarsly BiSeeMOS II.

SeeMos platform is dedicated to active vision and in particular to the early vision process. Thus, the SeeMos platform which constitutes an embedded system is composed of a modular hardware and a software design.

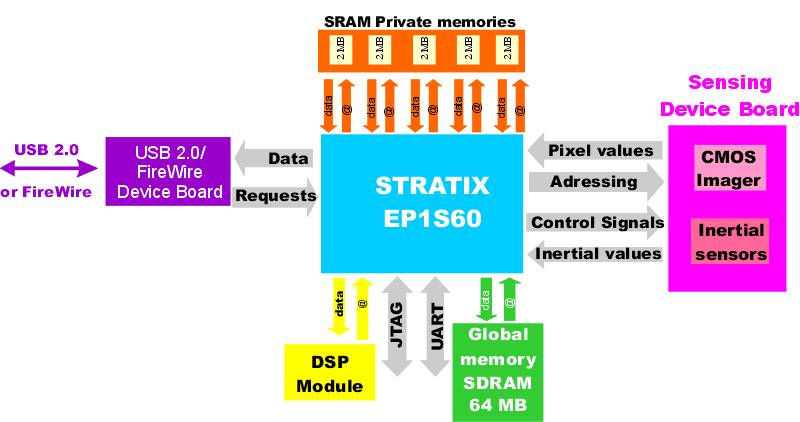

The main feature of this platform is an architecture based on FPGA, CMOS imager, Inertial devices, High speed communication and a DSP-based Codesigned board.

The main purpose of our architecture is to allow the implementation of early vision processes as in the human or primate visual system. In these systems it is well known that the first neural layers (in the retina) pre-filter the visual data flow in order to select only the conspicious information.

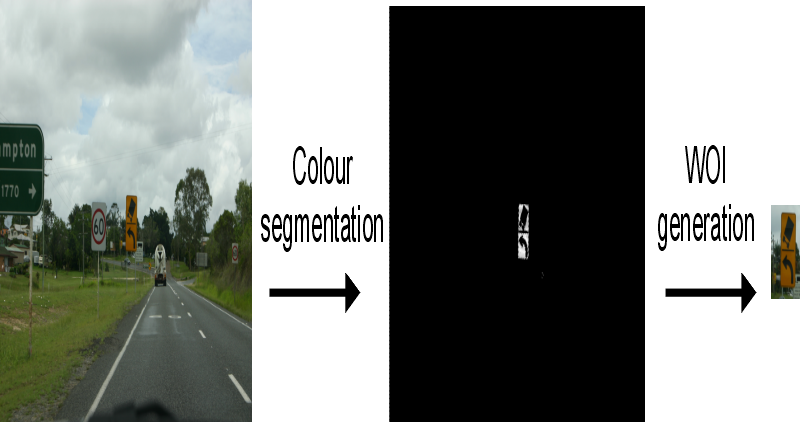

This Prefiltering step needs strong parallelization, on one hand to respect real-time constraints, and on the other hand because of the intrinsic characteristics of the algorithms. For exemple, some classical algorithms in an attention task used to elaborate an efficient saliency map are motion detection, Gabor filters, and color segmentation. However, the characteristics of particular visual tasks may require dedicated image processing and only an FPGA approach allows such flexibility. For architectures such as these, a Stratix EP1S60 from Altera has been chosen. The need for strong parallelization was what led us to connect 5x2MB SRAM synchronous memory blocks. In our approach, the high-level processing has to be performed on a host computer rather than on the embedded system.

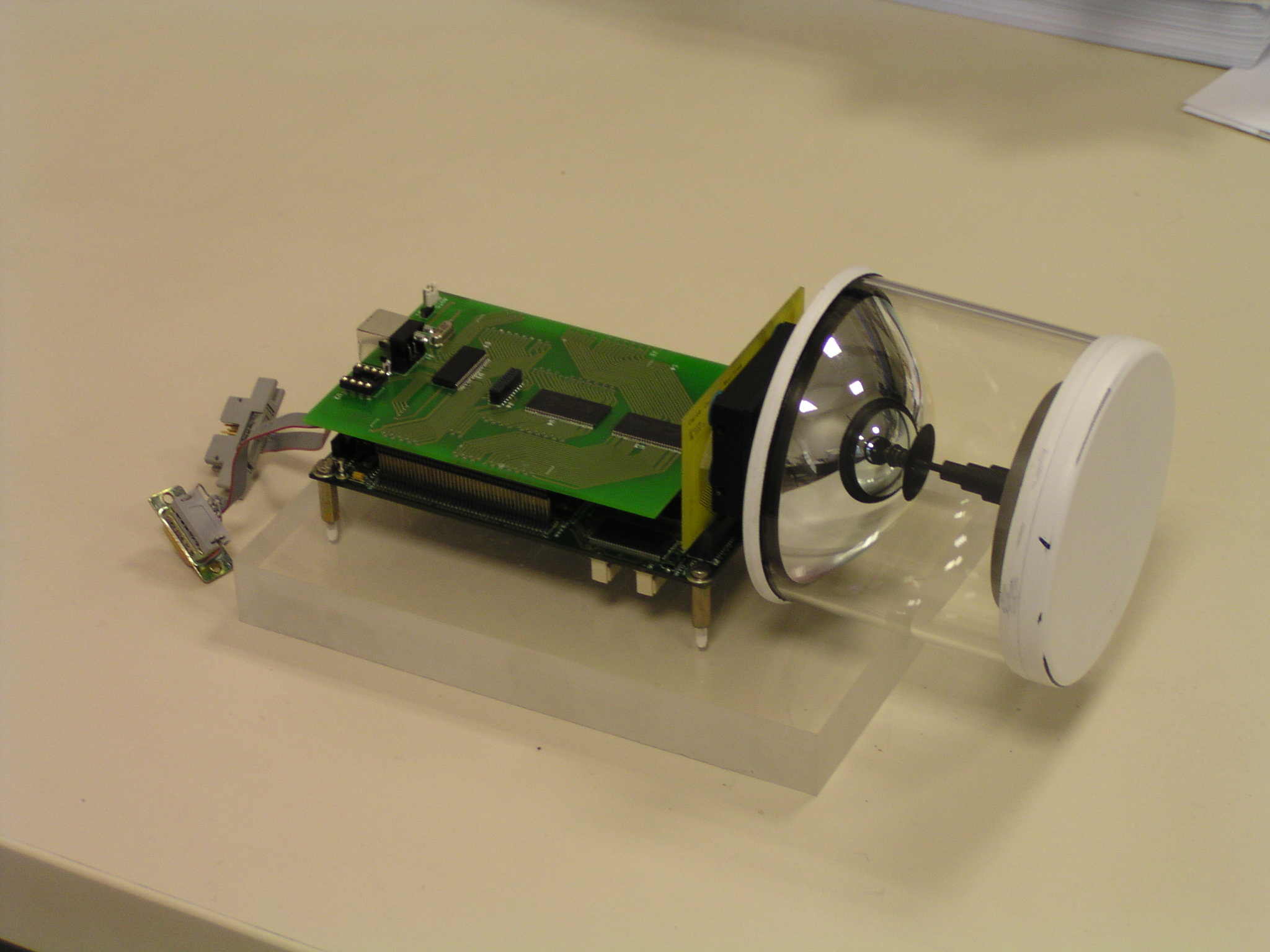

OmniMOS is an old smart camera dedicated to omni-directional vision. It builds with a fovea-based image sensor associated to paraboloidal reflector.

The image sensor named "Amovite" and built by Fillfactory provided a foveal image. In such sensor, the photosites are arranged in concentric rings and with a size varying linearly with the distance from the geometric center.

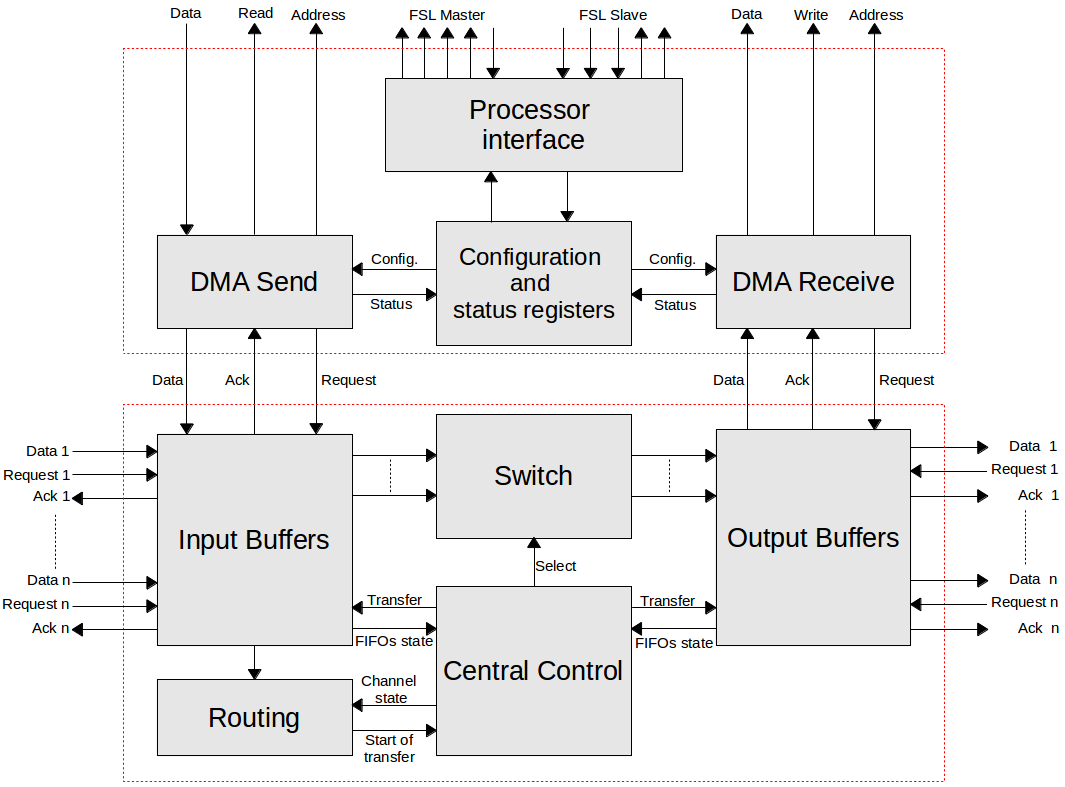

The router is associated to a DMA (Direct Memory Access) module. DMA enables both hardware packet injection from local node memory into the network, and symmetrically, hardware packet rejection from the network into local node memory. Packet headers are automatically added and removed by the DMA hardware module. The router uses a wormhole routing technique using buffers that enable to handle a small part of a packet. We have chosen this routing technique in order to minimize communication latency.

More information will be posted regarding the IP (VHDL code, Datasheet, TestBench,..).